STM32WB IWDG Function Introduction

IWDG Function

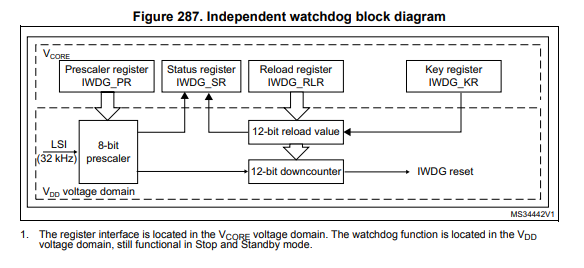

In the previous chapter, it was mentioned that standby mode can be woken up through IWDG. The functional block diagram of the Independent Watchdog (IWDG) is shown below. In fact, the IWDG is a decrementing counter. When the value of the counter is reduced to zero, IWDG generates a reset signal, and the system restarts. To avoid generating a watchdog reset, the counter needs to be reloaded before it reaches zero, i.e. “feeding the dog”. When the program fails to refresh the counter, the counter decreases to zero, and the system restarts to prevent the program from continuing to run incorrectly. PS: Since its clock is an independent 32-kHz low-speed internal RC oscillator (LSI), it remains active even if the main clock fails.

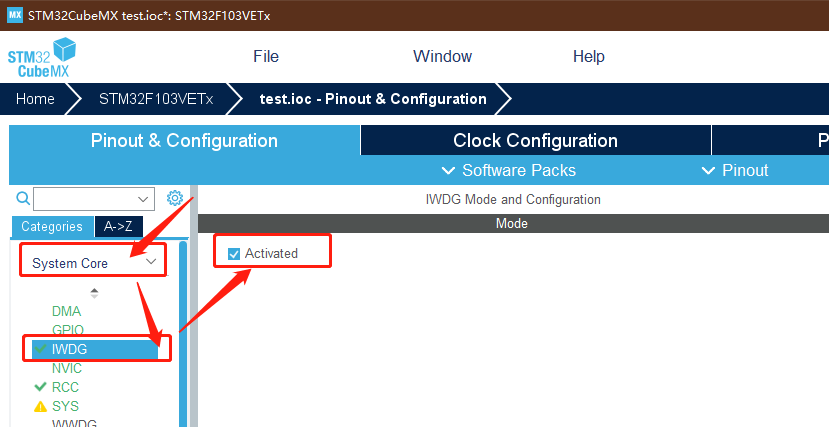

IWDG STM32CubeMX Setting

- IWDG counter clock prescaler Set the prescaler value to 32

- IWDG down-counter reload value the reload register value to 1000

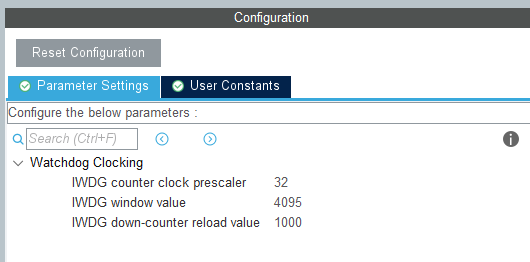

The timeout period is given by Tout = (4*2^prv) / LSI * rlv (s), where prv is the value of the prescaler register and rlv is the value of the reload register.

From the diagram, we know that LSI is 32 KHz. When prv is set to IWDG_PRESCALER_32 and rlv is set to 1000, Tout=32/32*1000=1s, which means a timeout overflow of 1 second is set.。

MX_IWDG_Init();

/* USER CODE BEGIN 2 */

printf("\n\r***** IWDG Test Start *****\n\r");

/* USER CODE END 2 */

/* Infinite loop */

/* USER CODE BEGIN WHILE */

while (1)

{

printf("\n\r Refreshes the IWDG !!!\n\r");

HAL_IWDG_Refresh(&hiwdg);

HAL_Delay(800);

/* USER CODE END WHILE */

/* USER CODE BEGIN 3 */

}

Since the timeout overflow is set to 1 second, the watchdog is fed every 800 milliseconds here: HAL_IWDG_Refresh(&hiwdg).